- 商業趨勢

- 一顆氣泡毀掉1.8億!印能科技靠「除泡」稱霸全球九成市場

一顆氣泡毀掉1.8億!印能科技靠「除泡」稱霸全球九成市場

一顆微小氣泡可能讓價值1.8億元的AI晶片報廢!台灣印能科技開發高壓真空除泡系統,全球市佔率達九成,成為台積電CoPoS平台首波供應商。深入解析先進封裝為何不能有氣泡,以及印能如何用四大技術稱霸市場。

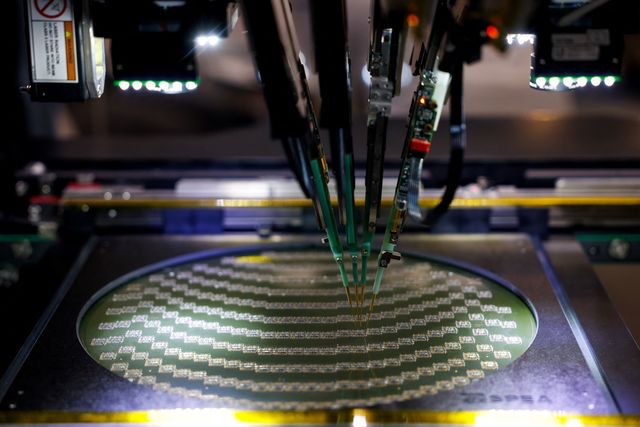

印能科技成功打入台積電首波 CoWoS 供應商。|Photo Credit: Reuters / TPG Images

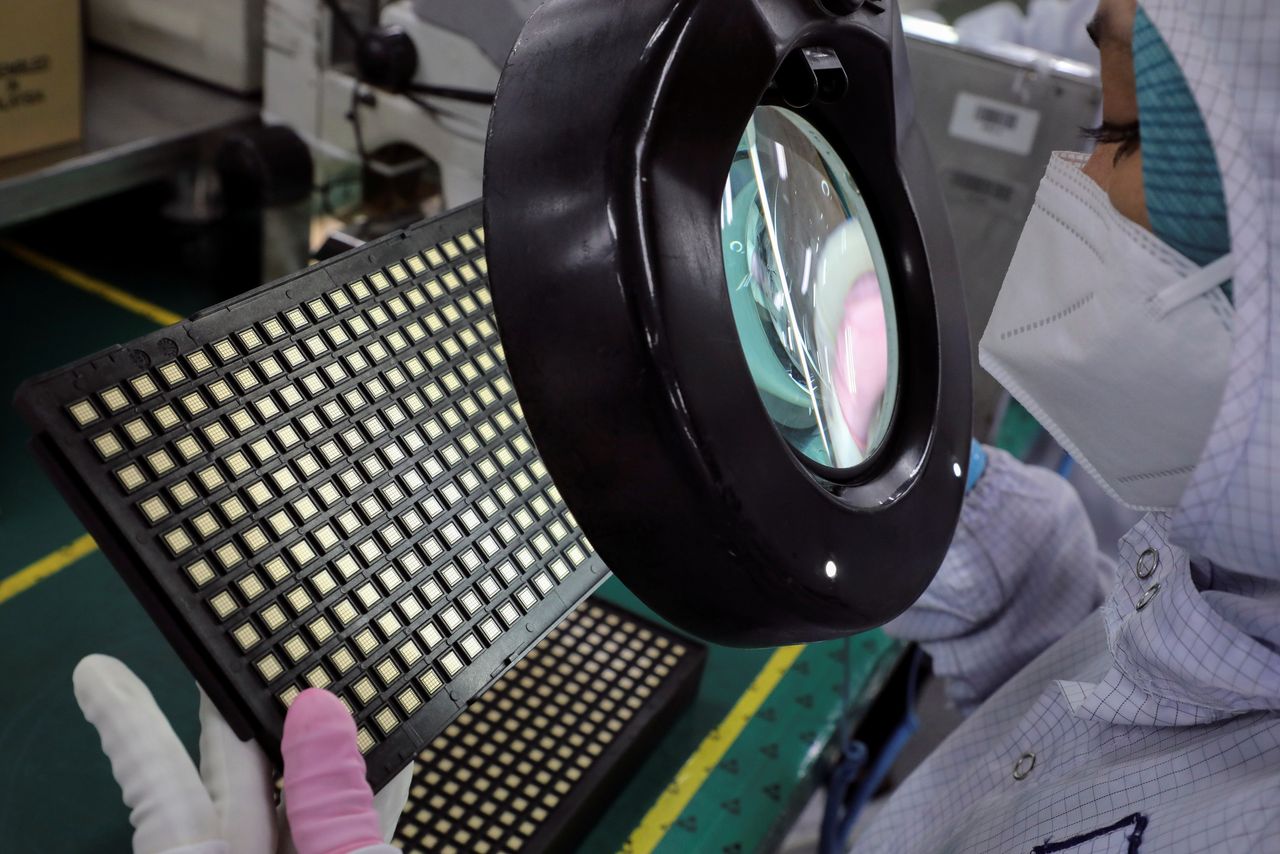

印能科技專注於先進封裝製程中的「除泡」設備,其高壓真空除泡系統(VTS)在全球市佔率達九成。隨著 AI 晶片對先進封裝需求持續攀升,該公司已被納入台積電 CoPoS 平台的首波供應商名單。

為什麼AI晶片怕氣泡?一顆氣泡如何毀掉1.8億元產品

要理解印能的價值,得先了解先進封裝製程中的痛點。

現在的 AI 晶片採用堆疊封裝技術,將多顆小晶片垂直堆疊在一起。在這個過程中,晶片之間需要填入膠材。如果膠材中殘留微小氣泡,當晶片高溫運作時,氣泡會膨脹,輕則造成訊號傳輸異常,重則直接撐裂晶片結構。

印能董事長洪誌宏曾舉例,他們曾協助客戶處理一爐 25 片晶圓的產品,價值高達 575 萬美元,約合新台幣 1.8 億元。在這種高單價的製程中,一顆氣泡就可能導致整爐報廢。洪誌宏形容:「在先進封裝裡,良率沒有 99 分,只有 0 分和 100 分的差別。」

印能的核心設備 VTS(高壓真空除泡系統),透過精準控制壓力與溫度,將膠材中的微小氣泡「逼」出來,確保封裝良率。

印能的四大技術:從除氣泡到1200瓦散熱挑戰

除了氣泡問題,印能的技術還涵蓋另外三個先進封裝的痛點。

第一是翹曲(Warpage),隨著晶片越做越薄、面積越做越大,製程中的熱脹冷縮容易導致晶片彎曲變形。印能開發的翹曲抑制系統(WSS),可在製程中維持晶片平整。

第二是高溫熔焊(Metal Joint),堆疊封裝需要透過金屬接點連接不同層的晶片,熔焊過程的溫度控制直接影響接點品質。

第三是散熱(Heat Dissipation),AI 晶片的功耗越來越高,散熱成為關鍵挑戰。印能目前正在開發一種可應對單顆晶片 1200 瓦高功率的「氣冷」測試設備。洪誌宏認為,雖然市場普遍看好液冷技術,但氣冷技術仍有發展空間,若能成功,可為客戶省下大量液冷建置成本。

印能將自身定位為「控制高壓真空中的熱流」的專家,上述四大問題都與此核心能力相關。

打入台積電!印能成為CoPoS平台13家供應商之一

2025 年 8 月,台積電推出下一代面板級先進封裝技術 CoPoS(Chip-on-Panel-on-Substrate),印能入列首波供應商名單,成為 13 家廠商之一。

CoPoS 是為了因應 AI 晶片對電源管理和訊號傳輸更高要求而生的新平台,將晶片封裝在大型方形基板上,取代傳統圓形矽中介層,目標是提升高階 AI 晶片的產能與良率。該技術預計 2026 年試產,2028 至 2029 年量產。

除了台積電,印能的客戶還包括日月光、力成等封測大廠。隨著晶圓代工廠的 CoWoS 先進封裝產線滿載,超額需求外溢至封裝代工(OSAT)業者,各大封測廠紛紛擴建符合晶圓代工廠標準的產線。印能的設備因高度相容於這些製程規範,可快速導入新建產線,訂單動能隨之增強。

獲「工程界諾貝爾獎」:一台設備搞定兩道製程

印能的第四代產品「EvoRTS」曾獲得 R&D 100 Awards,該獎項有「工程界諾貝爾獎」之稱。

這套系統將「除泡」與「助焊劑殘留清除」兩個製程步驟整合為一,過去這兩件事需要分開處理,現在一台設備即可完成,同時達到節能減碳效果。對於重視 ESG 的國際客戶而言,這是額外的加分項目。

九成市佔的護城河:60項專利與技術獨佔性

截至 2025 年,印能在全球擁有超過 60 項專利,這是其技術護城河,但也意味著需要持續投入資源進行智財權的維護與攻防。

印能科技在先進封裝除泡設備領域的全球市佔率達九成,顯示其在特定利基市場具備領先地位。隨著 AI 晶片需求持續成長,先進封裝產能擴張,該公司短期內受惠趨勢明確。

不過,高度集中於單一技術領域也意味著業務多元化程度有限。未來若市場出現替代技術,或主要客戶調整供應鏈策略,都可能對其營運產生影響,印能目前積極布局矽光子(CPO)等新興領域,試圖擴大技術版圖,後續成效仍有待觀察。

常見問題 FAQ

為什麼先進封裝製程不能有氣泡?

AI晶片採用堆疊封裝技術,將多顆小晶片垂直堆疊。晶片之間需要填入膠材, 如果膠材中殘留氣泡,當晶片高溫運作時,氣泡會膨脹,造成訊號傳輸異常, 嚴重時直接撐裂晶片結構,導致整批產品報廢。

印能科技的除泡設備如何運作?

透過高壓真空除泡系統(VTS),精準控制壓力與溫度,將膠材中的微小氣泡 「逼」出來。這套系統全球市佔率達九成,是先進封裝製程的關鍵設備。

什麼是台積電的CoPoS技術?

CoPoS(Chip-on-Panel-on-Substrate)是台積電下一代面板級先進封裝技術, 將晶片封裝在大型方形基板上,取代傳統圓形矽中介層,目標是提升高階AI晶片 的產能與良率。預計2026年試產,2028-2029年量產。

除了除泡,印能還有什麼技術?

印能掌握四大先進封裝技術: 1.除泡:消除膠材中的微小氣泡 2.翹曲抑制:維持超薄晶片在製程中的平整度 3. 高溫熔焊:確保堆疊晶片間金屬接點品質 4. 散熱測試:開發可應對1200瓦高功率的氣冷測試設備

想了解最新國際商業趨勢但時間跟語言有限制?訂閱 Business Insider【Insider Talk】電子報,免費解鎖國外付費會員資格的深度文章!

延伸閱讀

責任編輯:羅弘旭 / 核稿編輯:林筠騏